## **Technical Publication Change Instructions**

Updated replacement pages and/or drawings are attached to these Change Instructions. Please remove and discard the corresponding pages and/or drawings, and replace them with the attached pages and/or drawings. Failure to make these replacements may result in loss of product efficiency and possible failure.

Page numbers no longer have an alpha suffix, the revision level will now have a numerical suffix denoting its difference. Specific changes are identified by change bars in corresponding margins. A replacement page with no suffix has not been changed but is included only because it is part of the changed page.

Replacement pages will become standard pages without a suffix in the next printing of this manual and the Front Matter, Table of Contents, Preface and Index will be updated at that point. For record purposes, you are encouraged to retain these change instructions as a permanent part of the manual. Record new changes in your manual section entitled "Record of Changes".

| Product:       | 50000B           | Manual:     | SERIES 5000B VXIBUS MICROWAVE<br>SYNTHESIZERS OPERATION MANUAL |                    |  |

|----------------|------------------|-------------|----------------------------------------------------------------|--------------------|--|

| Errata Issued: | July 24, 2001    | Errata #:   | 31797-A1                                                       |                    |  |

| Manual P/N:    | Manual Revision: | Print Date: | New Manual<br>Revision:                                        | Errata Print Date: |  |

| 31797          | Α                | April 2000  | A1                                                             | July 2001          |  |

Update your product technical manual. Replace the page(s) indicated below with their new revision level:

| ECO(s): | Replace Page(s): | Remark(s):                                                                                                                    |

|---------|------------------|-------------------------------------------------------------------------------------------------------------------------------|

|         | 1-1 thru 1-2     |                                                                                                                               |

|         | 2-1 thru 2-4     |                                                                                                                               |

|         | 2-7 thru 2-8     |                                                                                                                               |

|         | 2-11 thru 2-12   | N/A                                                                                                                           |

|         | 2-15 thru 2-16   | — N/A                                                                                                                         |

|         | 2-25 thru 2-26   |                                                                                                                               |

| 7932    | 3-5 thru 3-8     |                                                                                                                               |

|         | 3-11 thru 3-22   |                                                                                                                               |

|         | Entire Chapter 4 | Chapter 4 has to be entirely replaced, because of extended page and formatting of text, to fix this would affect readability. |

|         | 5-1 thru 5-2     | N/A                                                                                                                           |

|         | 5-5 thru 5-12    | IV/A                                                                                                                          |

|         | A-1 thru A-2     | Update to formatting in A.2.                                                                                                  |

# Introduction

### 1.1 Description

The Giga-tronics VXIbus Microwave Synthesizers produces microwave signals with a high degree of frequency accuracy, frequency resolution and spectral purity. These signals may be controlled in amplitude over a wide range and are capable of being modulated in AM, FM and pulse modes. The product is designed to be installed in a VXI frame and to operate in the VXIbus environment.

The Giga-tronics VXIbus product line is designed to take advantage of the building block characteristics of the VXI system. The synthesizer is divided into discrete, C-size modules. There are two basic modules, which must always be present in any system. The first required module is the Control module (Model 52000B). This single width unit provides an interface to the VXI bus system and generates control signals for all other Giga-tronics modules. These control signals use the 12 local bus lines of the P2 connector. The Control module also provides a number of analog reference signals via front panel connectors.

The other module required for a minimum system is the double-width Synthesizer module (various model numbers in the 50000B/51000B series). Microwave frequencies are synthesized from the signals supplied by the Control module. The Synthesizer module contains all required circuitry and components to generate, modulate, and level the RF output.

Adaptor modules may also be included for optional features to the system.

Complete performance specifications for each module are presented in Section 1.2 in this chapter.

#### 1.1.1 Items Furnished

In addition to options and/or accessories specifically ordered, items furnished with the instrument are as follows:

- 1 Operation Manual (P/N 31797)

- 1 Set of Reference Signal SMB-to-SMB cables (as required by modules)

- or more RF semi-rigid cables (as required by optional modules)

### 1.1.2 Items Required

A VXI mainframe which meets the power and cooling requirements of the modules is required. Appropriate output cabling, which is made to fit the female SMA output connector, can be ordered in the form of Accessory A001 (Cable Kit).

### 1.1.3 Tools and Test Equipment

Special tools are not required in order to operate Series 50000B instruments. Signal sources for external modulation should match the parameters outlined in the specifications in this chapter. Test equipment required for calibration and testing is described in Chapter 4 of the manual.

#### 1.1.4 Storage

Giga-tronics VXIbus modules should be stored in an environment free from excessive dust and dirt and where the temperature remains in the range of -40°C to +70°C.

### 1.1.5 Cooling

The specifications for individual modules define their cooling and airflow requirements. If the module is to be operated outside of a properly ventilated VXI frame, auxiliary air circulation is required, such as a small fan directed at the module.

### 1.1.6 Receiving Inspection

Use care in removing the instrument from the carton and check immediately for physical damage, such as bent or broken connectors on the front and rear panels, dents or scratches on the panels, broken extractor handles, etc. Check the shipping carton for evidence of physical damage and immediately report any damage to the shipping carrier.

Each Giga-tronics instrument must pass rigorous inspections and tests prior to shipment. Upon receipt, the instrument's performance should be promptly checked to ensure that it's operation has not been impaired during shipment.

Each module is shipped in an operational condition and needs only to be plugged into a VXI frame to be used. A warm-up time of twenty minutes is recommended.

### 1.1.7 Safety Precautions

When installing modules into the mainframe, be sure that the connectors are properly aligned before pushing the modules into place. Use gentle but firm pressure to insert the modules and make sure they are fully seated for proper operation. In addition, make sure that the modules are installed in the correct positions relative to one another (see Positioning Requirements in Chapter 2).

### 1.1.8 Returning an Instrument

If it is necessary to return the instrument to the factory, protect the instrument during reshipment by using the best packaging materials available. If possible, use the original shipping container. If the original container is not available, use a strong carton (350 lbs./sq.in. bursting strength) or a wooden box. Wrap the instrument in heavy paper or plastic before placing it in the shipping container. Completely fill the areas on all sides of the instrument with packaging material. Take extra precaution to protect the front and rear panels. Seal the package with strong tape or metal bands. Mark the outside of the package: **"FRAGILE — DELICATE INSTRUMENT"**.

If corresponding with the factory or the local Giga-tronics sales office regarding reshipment, please provide the model and serial number. If the instrument is being returned for repair, be sure to enclose all relevant information regarding the problem that has been found.

**NOTE:** If you are returning an instrument to Giga-tronics for service, first contact Customer Service so that a return authorization number (RMA) can be assigned via e-mail at **repairs@gigatronics.com** or at **800.444.2878** (The 800 number is only valid within the US). You may also try our domestic line at **925.328.4650** or Fax at **925.328.4702**.

# **Operation**

### 2.1 Installation

### 2.1.1 Control Module Address Settings

The Control module requires no pre-installation configuration and can be installed in any slot of the VXI frame (except Slot 0). Its VXI Logical Address is assigned by means of a DIP switch. The switch is accessible through an opening on the left side of the module.

The switch positions represent a binary number pattern from 0 to 255 (more than one bit switch can be set to 1). The bit switch nearest the bottom rail of the module is the least significant bit. The switch position marked **ON** (toward the back of the module) is tied to ground through a resistor and is interpreted as a binary 0. The **OFF** (forward) position is interpreted as a binary 1.

The factory setting for this address is all 1 bits (hex FF, decimal 255). In the VXI environment, this value specifies dynamic configuration, which means that at start-up the Slot 0 controller will first perform a roll call of fixed address devices and then assign free addresses to all dynamic configuration devices. This prevents address conflicts.

The Model 52000B Control module is the only Giga-tronics module recognized directly by the Slot 0 controller. All other Giga-tronics modules must be installed contiguously to the right of the Model 52000B Control module and are recognized via the VXI local bus (12 lines which are forwarded via the backplane and reserved for local purposes).

### 2.1.2 Address Settings for Other Modules

All of the other Giga-tronics modules require the selection of local addresses to differentiate them from one another. The address of each module is set by a row of switches (accessible from the outside of the module). However, in the case of a local address, these switches are not interpreted as a binary number. Only one of the eight switches should be in the ON (back) position at a time. The switches are labeled 0 - 7 and represent local addresses 0 - 7. Local addresses must be consecutive within a group of modules which work together.

The Synthesizer module should be placed to the immediate right of the Control module and should have the lowest address. The addresses of subsequent modules increase consecutively with the last module in the RF path having the highest address. The recommended arrangement is to set the Synthesizer module address to 0, the next module address to 1, and so on, so that the modules will be easy to identify for programming purposes.

Be sure that modules do not share the same address.

### 2.1.3 Inserting the Modules

After the module addresses are set, each module can be inserted into the VXI frame. Since the VXI local bus is not strapped across the entire width of the frame but only connects between the outer rows of the

### **Series 50000B VXIbus Microwave Synthesizers**

P2 connector in adjacent slots, all Giga-tronics modules must be installed in one contiguous block. Also note that the next slot to the right of the last Giga-tronics module will have data appearing on its local bus lines. This should not cause a problem unless a module placed in that position uses those pins.

It will not cause a conflict if a second Giga-tronics Control module is placed to the right of a block of Giga-tronics modules. The Control module does not connect to the left direction local bus.

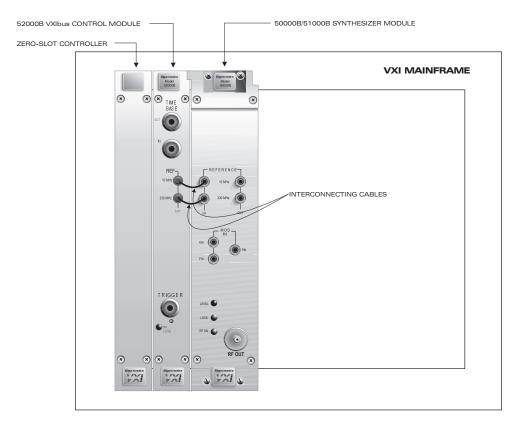

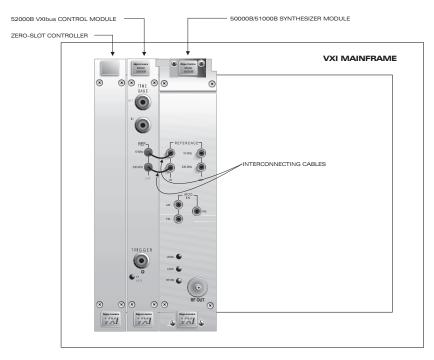

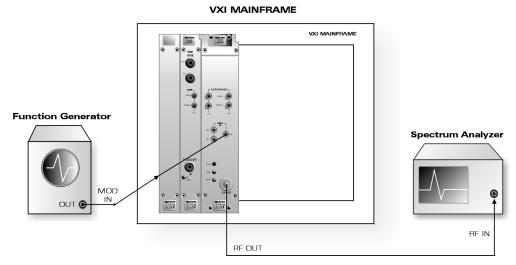

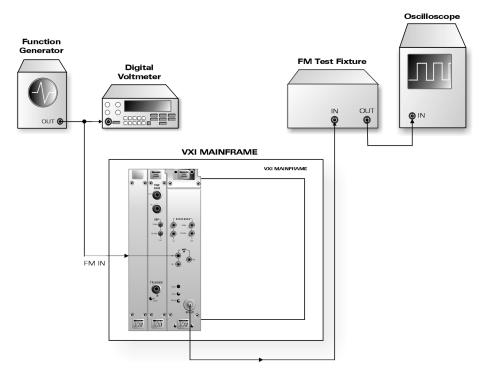

Figure 2-1: Module Mainframe Positions

#### 2.1.4 Interconnection

Once the modules have been inserted in the VXI frame, use the supplied coaxial cables to connect the 10 MHz and 330 MHz signals (these are timebase-derived reference signals). These cables are required for proper interconnection of the Control module and any subsequent Synthesizer modules.

Begin by connecting the Control module 10 MHz output to the 10 MHz input on the first Synthesizer module. Likewise connect the 330 MHz line (see Figure 2-1). All cable assemblies are identical and can be used in any position. If there is more than one Synthesizer module in the system, connect the two signal outputs of the first module to the inputs of the next.

If it is required to place some other Giga-tronics module between two Synthesizer modules, longer cables can be fabricated using SMB female type connectors and a length of appropriate 50 ohm coaxial cable. Cable length should be no greater than is necessary to bridge the gap.

### 2.1.5 External Inputs

I

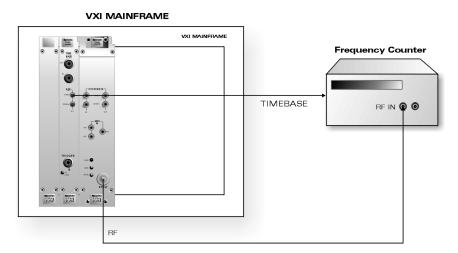

An external 10 MHz timebase can be connected to the Control module to allow the use of an external signal as a common system reference. The internal timebase is automatically disconnected when the external one is connected. The external timebase must have an amplitude of at least  $1.5~V_{p-p}$  and must be accurate to within  $1~x~10^{-6}$ .

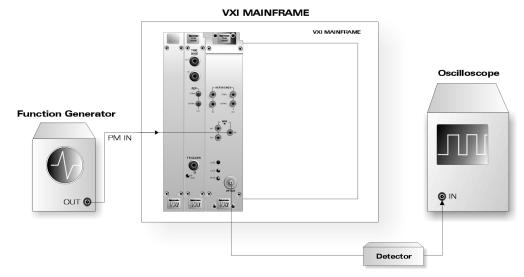

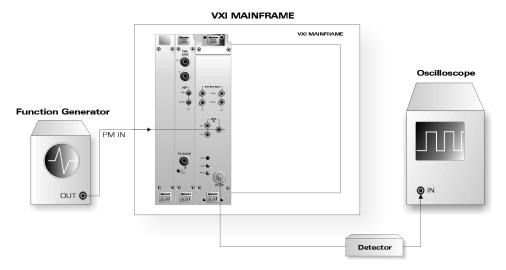

The Synthesizer module has inputs which accept external modulating signals for AM, FM and PM. See the specifications in Chapter 1 for input parameters. The Synthesizer module includes a 10-pin Sweep Input connector, which accepts sweep control signals.

#### 2.1.6 **Connections to the VXI Mainframe**

All modules connect to the backplane of the VXI mainframe through a pair of 96-pin connectors (P1 and P2). Pin assignments for these connectors are shown below.

**Table 2-1: VXI Backplate Pinouts**

| Pin<br>No. | P1 Connector |           | P2 Connector |          |       |          |

|------------|--------------|-----------|--------------|----------|-------|----------|

|            | Row A        | Row B     | Row C        | Row A    | Row B | Row C    |

| 1          | D00          | BBSY      | D08          | ECLTRG0  | +5V   | CLK10+   |

| 2          | D01          | BCLR      | D09          | -2V      | GND   | CLK10-   |

| 3          | D02          | ACFAIL    | D10          | ECLTRG1  | RSV1  | GND      |

| 4          | D03          | BG0IN     | D11          | GND      | A24   | -5.2V    |

| 5          | D04          | BG0OUT    | D12          | LBUSA00  | A25   | LBUSC00  |

| 6          | D05          | BG1IN     | D13          | LBUSA01  | A26   | LBUSC01  |

| 7          | D06          | BG10UT    | D14          | -5.2V    | A27   | GND      |

| 8          | D07          | BG2IN     | D15          | LBUSA02  | A28   | LBUSC02  |

| 9          | GND          | BG2OUT    | GND          | LBUSA03  | A29   | LBUSC03  |

| 10         | SYSCLK       | BG3IN     | SYSFAIL      | GND      | A30   | GND      |

| 11         | GND          | BG3OUT    | BERR         | LBUSA04  | A31   | LBUSC04  |

| 12         | DS1          | BR0       | SYSRESET     | LBUSA05  | GND   | LBUSC05  |

| 13         | DS0          | BR1       | LWORD        | -5.2V    | +5V   | -2V      |

| 14         | WRITE        | BR2       | AM5          | LBUSA06  | D16   | LBUSC06  |

| 15         | GND          | BR3       | A23          | LBUSA07  | D17   | LBUSC07  |

| 16         | DTACK        | AM0       | A22          | GND      | D18   | GND      |

| 17         | GND          | AM1       | A21          | LBUSA08  | D19   | LBUSC08  |

| 18         | ĀS           | AM2       | A20          | LBUSA09  | D20   | LBUSC09  |

| 19         | GND          | AM3       | A19          | -5.2V    | D21   | -5.2V    |

| 20         | ĪACK         | GND       | A18          | LBUSA10  | D22   | LBUSC10  |

| 21         | IACKIN       | SERCLK    | A17          | LBUSA11  | D23   | LBUSC11  |

| 22         | IACKOUT      | SERDAT    | A16          | GND      | GND   | GND      |

| 23         | AM4          | GND       | A15          | TTLTRIG0 | D24   | TTLTRIG1 |

| 24         | A07          | ĪRQ7      | A14          | TTLTRIG2 | D25   | TTLTRIG3 |

| 25         | A06          | ĪRQ6      | A13          | +5V      | D26   | GND      |

| 26         | A05          | ĪRQ5      | A12          | TTLTRIG4 | D27   | TTLTRIG5 |

| 27         | A04          | ĪRQ4      | A11          | TTLTRIG6 | D28   | TTLTRIG7 |

| 28         | A03          | ĪRQ3      | A10          | GND      | D29   | GND      |

| 29         | A02          | ĪRQ2      | A09          | RSV2     | D30   | RSV3     |

| 30         | A01          | ĪRQ1      | A08          | MODID    | D31   | GND      |

| 31         | -12V         | +5V STDBY | +12V         | GND      | GND   | +24V     |

| 32         | +5V          | +5V       | +5V          | SUMBUS   | +5V   | -24V     |

#### 2.3.3 Command Set

The command set for the HP-style syntax is listed in the following tables. The commands are discussed in alphabetical order with some related commands grouped together.

#### **Commands \*CLS through \*WAI (IEEE 488.2 Common Commands)**

See the SCPI section for more information about these commands.

Table 2-2: Commands \*CLS - \*WAI

| Command | Description                                            |

|---------|--------------------------------------------------------|

| *CLS    | Clear Status                                           |

| *ESE    | Event Status Enable                                    |

| *ESE?   | Event Status Enable Query                              |

| *ESR?   | Event Status Register Query                            |

| *IDN?   | Identify                                               |

| *OPC    | Operation Complete                                     |

| *OPC?   | Operation Complete Query                               |

| *RST    | Reset                                                  |

| *SRE    | Status Register Enable                                 |

| *SRE?   | Status Register Enable Query                           |

| *STB?   | Status Byte Query                                      |

| *TST?   | Self-Test Query (see the self-test commands, TA etc.). |

| *WAI    | Wait-to-Continue                                       |

#### **Commands AM0 through FM1 (Miscellaneous)**

Table 2-3: Commands AM0 - FM1

| Command | Description                                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------|

| AMO     | Deactivate external AM.                                                                                        |

| AM1     | Activate external AM.                                                                                          |

| AMF0    | Deactivate external fast AM.                                                                                   |

| AMF1    | Activate external fast AM.                                                                                     |

| CIIL    | Switch to CIIL language.                                                                                       |

| CW d t  | Select the CW (fixed frequency) mode.                                                                          |

| DN      | Down step of frequency or power level, depending on whether the last command was CW (Frequency) or PL (Power). |

| [       | Down step of frequency or power level, depending on whether the last command was CW (Frequency) or PL (Power). |

| FM0     | Deactivate external FM.                                                                                        |

| FM1     | Activate external FM.                                                                                          |

#### **Commands GA through GR (FSD Commands)**

Frequency Sweep Digital (FSD) commands permit the setup then activation of digital frequency sweep. Depending on the sweep triggering method chosen, the sweep can begin immediately upon receipt of the activation command or after the activation command followed by a definable hardware trigger signal. The sweep can be single or continuously repetitive. The next frequency is obtained either by adding the step size increment to the last frequency or by retrieving the next frequency value from a list stored in memory.

Table 2-4: Commands GA - GR

| Command | Description                                                                                                                                                                                                                                                                                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GA d t  | Set the sweep start frequency to d GHz. Default: minimum frequency.                                                                                                                                                                                                                                                                                            |

| GB d t  | Set the sweep stop frequency to d GHz. Default: maximum frequency.                                                                                                                                                                                                                                                                                             |

| GC d t  | Set the frequency step size to d GHz. Default: 1 GHz.                                                                                                                                                                                                                                                                                                          |

| GD d t  | Set the dwell time to d seconds. Default: 1 s.                                                                                                                                                                                                                                                                                                                 |

| GEI     | Start the sweep immediately upon receipt of a GG command (this is the default sweep triggering mode).                                                                                                                                                                                                                                                          |

| GEWF    | Start the sweep (following receipt of a GG command) when the hardware trigger input goes to the FALSE level (0 V).                                                                                                                                                                                                                                             |

| GEWT    | Start the sweep (following receipt of a GG command) when the hardware trigger input goes to the TRUE level (+5 V).                                                                                                                                                                                                                                             |

| GFC     | Select the continuous sweep mode (the sweep repeats automatically).                                                                                                                                                                                                                                                                                            |

| GFR     | Select the retriggerable single sweep mode (the sweeper will respond to another trigger occurring after completion of the sweep).                                                                                                                                                                                                                              |

| GFS     | Select the single sweep mode (the sweeper will NOT respond to another trigger occurring after completion of the sweep).                                                                                                                                                                                                                                        |

| GG      | Start the sweep. This command should be entered only after all the setup commands have been entered with the desired values. If the GEI command was sent previously, the GG command will cause the sweep to begin immediately. If the GEWF or GEWT command was sent, the GG command will cause the sweeper to wait for the appropriate hardware trigger input. |

| GH      | Halt the sweep, leaving the frequency at the last stepped value (NOTE: a CW command will also halt the sweep).                                                                                                                                                                                                                                                 |

| GIM     | Memory increment mode: increment the frequency by going to the next nonzero frequency stored in an array of up to ten memory locations (see the GJ command). The start frequency, stop frequency, and step size have no effect in this mode, but the dwell time does apply.                                                                                    |

| GIN     | Normal increment mode: increment the frequency by adding the defined step size to the last frequency (see the GC command). The start frequency, stop frequency, step size, and dwell time all apply in this mode.                                                                                                                                              |

| GJndt   | Save a sweep frequency (d) at memory location n (the range of values for n is 0 - 9). If the value saved at any memory location is zero, that memory location will have no effect on the sweep.                                                                                                                                                                |

| GK      | Clear all saved sweep frequencies from memory (see the GJ command).                                                                                                                                                                                                                                                                                            |

| GR      | Resume a sweep that was halted by a GH command.                                                                                                                                                                                                                                                                                                                |

#### **Commands TA through TSD (Self Test Commands)**

These commands all relate to the instrument's self-test routine.

Table 2-9: Commands TA - TSD

| Command | Description                                                                                                                                                                             |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TA      | Abort the test.                                                                                                                                                                         |  |  |

| TFB d t | Set the beginning frequency for the test to d. Default: minimum frequency.                                                                                                              |  |  |

| TFE d t | Set the ending frequency for the test to d. Default: maximum frequency.                                                                                                                 |  |  |

| TFS d t | Set the frequency step size for the test to d. Default: 1 GHz.                                                                                                                          |  |  |

| TFQ?    | Test frequency quit query (at what frequency did the test stop?). The test quits when a failure is detected. Default: 0 (test not yet run).                                             |  |  |

| TPC d t | Set the coarse power level for the test to d dBm. This specifies the setting of the step attenuator (from 0 dBm to maximum attenuation in 10 dB steps) during the test. Default: 0 dBm. |  |  |

| TPF d t | Set the fine power level for the test to d dBm. This specifies the setting of the leveling loop in 0.1 dB increments from -20 dBm - +20 dBm. Default: maximum leveled power.            |  |  |

| TSB?    | TST Status Binary Query.                                                                                                                                                                |  |  |

| TSD?    | TST Status Decimal Query.                                                                                                                                                               |  |  |

|         | Related Commands                                                                                                                                                                        |  |  |

| *TST?   | Self-Test Query                                                                                                                                                                         |  |  |

| RT      | Run self-test is a lock-and-level test of the synthesizer operation across a defined frequency range.                                                                                   |  |  |

The \*TST? command (an IEEE 488.2 Common Command) will preserve (it will save and later restore) these states:

**RFx** RF On/Off state

**CWx** CW Frequency value

**PCx** Power Level (Coarse) value

**PFx** Power Level (Fine) value

The test will then switch in the maximum step attenuation before doing its own testing to not damage any user circuitry at the RF output connector. The Power Level (fine) value during the test will be the maximum output value for the unit (usually 10 dBm), but the Power Level (coarse) is usually -90 dB. The connector output power is the sum of the two, which is small enough that it presents no risk of damage.

The \*TST? command always returns a decimal value result. If the returned value is 0, the test ran without errors. If not, the value is the sum of a series of weights as will be explained later.

The RT command resembles the \*TST? command but differs in two respects. The RT command does not reply (separate commands are provided to request results afterward.) The RT command stops at its last frequency, and does not remember the original frequency from before the test was run.

You must separately request the results of the RT command. You might also want to request again the reply of the \*TST? command in a different format. Two queries are provided for different style results.

The TSB? (Test Status Binary) query requests the result as a series of ASCII characters; each is either a 1 or a 0. The characters are in order and each one has a specific meaning. For any condition, 1 means the particular condition is satisfactory and 0 means it is not satisfactory. A test that runs without errors will return a TSB? of 111111111.

The TSD? (Test Status Decimal) query requests the same result expressed as a decimal number. If the returned value is 0, the test ran without errors. If not, the value is the sum of a series of weights which depend upon what type of hardware makes up the device. The inclusion of a particular condition's weight in the sum means the condition is not satisfactory.

The bit/weight meanings in the test status reply are the same whether the result is queried by a TSB? or a TSD? command, as illustrated in Table 2-10.

Table 2-10: Bit/Weight Meanings

| Bit | Weight | Meaning                   |

|-----|--------|---------------------------|

| 7   | 128    | Leveled                   |

| 6   | 64     | Downconverter Loop Locked |

| 5   | 32     | 110 MHz Loop Locked       |

| 4   | 16     | Output Loop Locked        |

| 3   | 8      | 300 MHz Loop Locked       |

| 2   | 4      | 80 MHz Loop Locked        |

| 1   | 2      | (not used)                |

| 0   | 1      | (not used)                |

If you inadvertently enter a very small step size and then start the test running, the abort command (TA) provides a way of stopping it before completion. The test is simply stopped. If you had issued the \*TST? command, no reply will occur after abort. You must manage the clearing of your expected reply.

With the \*TST? command, you simply wait for the reply. With the RT command, you must be sure the test is done before requesting its status via TSB? or TSD?. The easiest way to do this is by using the \*WAI command to wait until the test is done. You might prefer \*OPC or \*OPC?. Current firmware requires that the coordination command be on its own command line; likewise for the following TSB? or TSD? command.

#### Commands UL0 through 1 (Miscellaneous)

Table 2-11: Commands UL0 through ]

| Command | Description                              |

|---------|------------------------------------------|

| UL0     | Unleveled mode off                       |

| UL1     | Unleveled mode on                        |

| UP      | Up step for CW (Frequency) or PL (Power) |

| ]       | Up step for CW (Frequency) or PL (Power) |

### 2.5 SCPI Syntax

The SCPI syntax is now implemented in the 50000B Series. It includes the IEEE 488.2 Common commands, status reporting, error reporting, and table-specified defaults at power-up or \*RST.

#### 2.5.1 SCPI Command Format

Details of typography (such as indentation, case, and punctuation) are very significant in SCPI and must be attended to with great care. The typographic conventions employed in the SCPI command tables which follow are summarized here.

Colons indicate changes of level in the SCPI tree structure. If a command is represented in the format ALPHA:BETA:GAMMA, then BETA is one level down from ALPHA, and GAMMA is two levels down from ALPHA. If ALPHA is printed at the left margin, ALPHA is at the root level. In the command tables, indentation indicates relative levels.

Commands can be entered in upper or lowercase. However, only required letters are in upper case in the command table. If you enter more than the required letters, you must enter the entire command (if the command is INITiate, you may use either INIT or INITIATE, but INITI is invalid).

If a command is shown in square brackets, it is an implied command and can be omitted (the brackets are not part of the command and should be omitted even if the command itself is entered). An implied command is the default command among the commands available at its level. For example, in the case of the command INITiate:[IMMediate], the immediate mode is the default mode, so entering INIT has the same effect as entering INIT:IMM.

Because you can query any value that you can set, most commands also exist in a query form (signified by adding a question mark to the end of the keyword). The command tables do not contain separate listings for queries except in the case of commands that exist only in the query form. If there is a command ALPHA, you can assume that there is also an ALPHA? query unless the table entry includes the statement NO QUERY. Some commands are events that cause something to happen at a particular time but do not create a setting or value to be checked afterwards. Consequently, they have no query form.

Some commands require a parameter. The parameter types are:

BOOL: A Boolean (true or false) condition. Enter

```

ON or 1 for TRUE;

OFF or 0 for FALSE.

```

VAL:A numeric value or a qualitative term which represents a numeric value. Enter:

```

sign (optional),

digits,

decimal point (optional),

E xx (optional),

units suffix (optional).

Or enter MIN, or MAX.

```

Or enter UP, or DOWN (these only change the synthesizer's output frequency or output power level).

NUM: A number (typically represents register bit settings in the form of a decimal integer).

There are also discrete parameters. These are options to be chosen from a limited selection. For example, the TRIGger:SLOPe command has three possible discrete parameters to chose from (POSitive, NEGative, and NONe). The beginning of a parameter must be preceded by a space. The default units suffixes are DBM for power and HZ for frequency (the other suffixes for frequency are GHZ, MHZ, and KHZ).

#### 2.5.2 SCPI Commands

Tables 2-13 through Table 2-17 list the SCPI commands with notes on parameter types, initial values, and whether or not a query form of the command exists. The effect of the command is explained below each command listing. Many of these commands refer to the Status System, which is discussed in detail in Section 2.6. Commands beginning with an asterisk are IEEE 488.2 Common Commands.

Table 2-13: SCPI Commands CLS - TST

| Keyword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Parameter<br>Type                                                                                                                                        | Initial<br>Value                    | Query<br>Form?                             |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------|--|--|--|

| *CLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | none                                                                                                                                                     | none                                | no                                         |  |  |  |

| (Clear Status Command) This command clears the event reg<br>Register and the Error/Event Queue.                                                                                                                                                                                                                                                                                                                                                                                             | (Clear Status Command) This command clears the event registers in all status groups. It also clears the Event Status Register and the Error/Event Queue. |                                     |                                            |  |  |  |

| *ESE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NUM                                                                                                                                                      | 0                                   | yes                                        |  |  |  |

| (Standard Event Status Enable Command) This command ma<br>Status Register to generate service requests. The query for<br>Event Status Register have been enabled to generate service<br>represents the register's bit settings.                                                                                                                                                                                                                                                             | m (*ESE?) determi                                                                                                                                        | ines which change                   | s in the Standard                          |  |  |  |

| *ESR?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | none                                                                                                                                                     | 0                                   | query only                                 |  |  |  |

| (Standard Event Status Register Query) This command causes the event register of the Standard Event Status Register group to be read and transmitted over the bus                                                                                                                                                                                                                                                                                                                           | causes the event register of the Standard Event Status                                                                                                   |                                     |                                            |  |  |  |

| *IDN?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | none                                                                                                                                                     | none                                | query only                                 |  |  |  |

| (Identification Query) The response takes the form of four A: Manufacturer, (2) Model, (3) Serial Number, and (4) Firmwar 3 and 4 are filled by zeros if the data is not available.                                                                                                                                                                                                                                                                                                         | SCII fields separat<br>e Level or Equival                                                                                                                | ed by commas. Thent. Fields 1 and 2 | ne fields are: (1)<br>are required; fields |  |  |  |

| *OPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | none                                                                                                                                                     | none                                | yes                                        |  |  |  |

| (Operation Complete Command) This command causes the Operation Complete bit (that is, Bit 0 of the Standard Event Status Register) to be set to 1 when all pending selected device operations have been finished. The query form (*OPC?) places an ASCII character 1 into the device's output queue when all pending selected device operations have been finished. Unlike the *OPC command, the *OPC? query does not affect the OPC Event bit in the Standard Event Status Register (ESR). |                                                                                                                                                          |                                     |                                            |  |  |  |

| *RST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | none                                                                                                                                                     | none                                | no                                         |  |  |  |

| (Reset Command) This command sets the device-specific functions to a known state (the power-on state) that is independent of the past-use history of the device. The command does not reset any part of the status reporting system.                                                                                                                                                                                                                                                        |                                                                                                                                                          |                                     |                                            |  |  |  |

| *SRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NUM                                                                                                                                                      | 0                                   | yes                                        |  |  |  |

| (Service Request Enable Command) This command makes it possible for service requests to be generated by specified bits of the Status Byte Register. The query form (*SRE?) determines which bits of the Status Byte Register have been enabled to generate service requests.                                                                                                                                                                                                                |                                                                                                                                                          |                                     |                                            |  |  |  |

| *STB?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | none                                                                                                                                                     | none                                | query only                                 |  |  |  |

| (Status Byte Query) This command causes the event register transmitted over the bus. It also causes the register to be clearly                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                          | te Register group t                 | o be read and                              |  |  |  |

| *TST?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | none                                                                                                                                                     | none                                | query only                                 |  |  |  |

| (Self-Test Query) This command causes the synthesizer to perform a self-test routine. See the notes below concerning Self-Test.                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                          |                                     |                                            |  |  |  |

### 2.5.6 Sample SCPI Commands

Table 2-19 shows some examples of brief SCPI commands:

**Table 2-19: Sample SCPI Commands**

| Command       | Meaning                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|

| *IDN?         | Query instrument identification (response format: maker,model,serial#,firmware version; (sample response: Giga-tronics,50000,048256,75). |

| *RST          | Reset system.                                                                                                                            |

| OUTP OFF      | Turn off RF output.                                                                                                                      |

| AM:STAT OFF   | Turn off external amplitude modulation.                                                                                                  |

| AM:STAT?      | Query external amplitude modulation (sample response: 0).                                                                                |

| POW -9.2      | Set output power to -9.2 dBm.                                                                                                            |

| POW?          | Query output power (sample response: -9.2).                                                                                              |

| FM:STAT OFF   | Turn off external frequency modulation.                                                                                                  |

| FM:STAT?      | Query external frequency modulation (sample response: 0).                                                                                |

| FREQ 6.1GHZ   | Set output frequency to 6.1 GHz                                                                                                          |

| FREQ?         | Query output frequency (sample response: 610000000).                                                                                     |

| PULM:STAT OFF | Turn off external pulse modulation.                                                                                                      |

| PULM:STAT?    | Query external pulse modulation (sample response: 0).                                                                                    |

### 2.6 SCPI Status System

#### 2.6.1 Introduction

I

The SCPI standard includes a system for monitoring the status of the instrument. Much of this status system is imported from the IEEE 488.2 standard. Status monitoring is accomplished by means of several registers which can be read from (or in some cases written to). Registers of various kinds are combined into status groups and the status groups are nested: the output bits of a status group are summarized by a logical-OR gate. The summary output becomes one of several inputs to another status group. The various groups and registers are described in detail below.

SCPI terminology is not consistent. The distinction between a register and a group of registers is often ignored. Some status groups are called status registers. This manual does not attempt to correct SCPI's choice of words, but confusions of this kind will be pointed out where they occur.

### 2.6.2 Registers, Bit Numbers, and Decimal Weights

When a register is read, its bit settings are converted into a single decimal number for transmission over the interface. The decimal weights for the various bits are shown in Table 2-20 below:

Table 2-20: Bit Numbers and Decimal Weights

| Bit:    | 7   | 6  | 5  | 4  | 3 | 2 | 1 | 0 |

|---------|-----|----|----|----|---|---|---|---|

| Weight: | 128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 |

If Bit 0 (the least significant bit) is ON, its weight is 1. If Bit 7 (the most significant bit) is ON, its weight is 128. If 0 and 7 were the only bits ON, the register would have a decimal value of 129 (the sum of the weights). If all bits were ON, the register would have a decimal value of 255.

**NOTE:** Although SCPI defines some registers as having 16 bits, Giga-tronics makes use of only the lowest 8 bits of any register. Therefore, every register can be treated as if it contained only 8 bits.

To determine which bits are on from the decimal value, find the largest weight that does not exceed the decimal value. Subtract that weight from the value and mark that bit ON. Continue subtracting weights, and marking the associated bits ON until the decimal value is reduced to zero.

#### **EXAMPLE:**

The decimal value is 235.

Subtract 128 and mark Bit 7 ON. The decimal value is now 107.

Subtract 64 and mark Bit 6 ON. The decimal value is now 43.

Subtract 32 and mark Bit 5 ON. The decimal value is now 11.

Subtract 8 and mark Bit 3 ON. The decimal value is now 3.

Subtract 2 and mark Bit 1 ON. The decimal value is now 1.

Subtract 1 and mark Bit 0 ON. The decimal value is now 0.

Conclusion: Bits 7, 6, 5, 3, 1, and 0 are ON. Bits 4 and 2 are OFF.

This procedure is done in reverse in order to convert bit settings to a decimal value. Add together the decimal weights (as shown in Table 2-20) for each bit which is ON to find the equivalent decimal value.

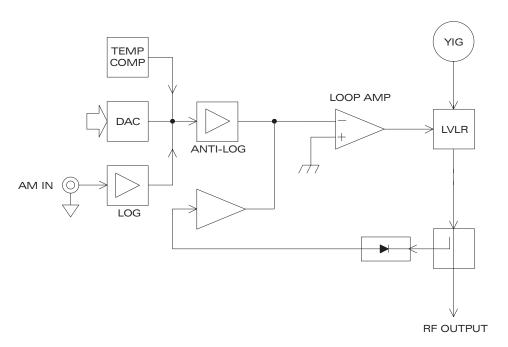

### 3.2 Amplitude Control

Amplitude control of the Synthesizer output is adjusted by a combination of fixed-step attenuation and closed-loop leveling (in the ALC). The fixed-step attenuation is done by a step attenuator providing up to 90 dB of attenuation in 10 dB increments. Closed-loop leveling is accomplished through Automatic Leveling Control (ALC), which provides fine adjustment in 1 dB increments.

#### 3.2.1 The ALC Circuit

The ALC is basically a loop amplifier with multiple inputs. One of the inputs takes feedback from the level detector (a circuit that returns a negative voltage proportional to the square of detected power). The RF measured by the detector is coupled from the output path by a circuit in the RF module. The detector signal is amplified and applied to the summing junction of the leveling loop amplifier; it is a variable input in that it changes in response to the loop amplifier output.

Figure 3-3: Amplitude Control

Another input into the ALC is the reference input. The reference input is a composite of three signals: a correction voltage from the temperature compensation circuit (PC board A3), a fixed leveling input (which the Control module programs by means of a digital to analog converter) and the AM signal from the front panel input. If present, the AM signal is processed by a logarithmic amplifier in order to give it the same logarithmic characteristic as the other two inputs. Then, all three signals can be combined by a summing amplifier; the combined signal is processed by an anti-logarithmic amplifier on its way to the loop amplifier.

The ALC output is sent to an amplifier which drives the PIN diode leveler so as to balance the reference input against an equal and opposite variable feedback input. In other words, the leveler adjusts RF power until the detector feedback input just cancels the other input to the loop amplifier.

In setting the leveling reference, through the programming of a digital to analog converter, the Control module includes compensation factors from a level-characterization table (stored in a PROM in the Synthesizer module). This data is individual to each synthesizer system and is compiled during production testing.

### **Series 50000B VXIbus Microwave Synthesizers**

#### 3.2.2 Amplitude Modulation

The AM input to the level control circuit supplies the leveling loop amplifier with a variable, rather than a fixed leveling reference. The variable reference is processed by a log amplifier in order to match the logarithmic characteristics of the computer leveling reference and the temperature compensation input. The level control circuit furnishes a modulated control voltage to the leveler in the RF module to match the modulation of the reference input. The result is an amplitude modulated RF output with a modulation depth of at least 20 dB.

#### 3.3 Pulse Modulation

Pulse modulation is performed by means of path-switching circuits in the RF module. Depending on output bandwidth, there will be up to five filter paths through the module (only one is active at a given time). PIN diode circuits switch these lines on and off; pulse modulation is accomplished by shutting off the active path intermittently. (A positive voltage at the filter line control pin on the outside of the module shuts the path off.) By this method, an on/off ratio of greater than 80 dB can be achieved.

### 3.4 Frequency Modulation

Frequency modulation of the RF output is achieved by modifying the fine tuning of the YIG oscillator. The current supply to the YIG's fine tuning coil is controlled by the FM driver (Part of A2), which in turn, is controlled by the output phase lock loop circuit (Part of A2). Normally, the PLL driver output, suitably filtered and amplified, is derived from the outputs of the phase comparator. However, during operation in the FM mode, this phase comparator signal is summed with a modulation signal. The outcome is a modulated drive resulting in a frequency modulated output from the YIG oscillator.

### 3.5 Frequency Synthesis

The output frequency is produced by a YIG oscillator. Coarse tuning of the YIG is done through the YIG driver (A3). The A3 circuit board supplies a programmable current source which the Control module adjusts by means of a digital to analog converter and amplifier. This current source, connected to the YIG tuning coil, can bring the YIG frequency within 50 MHz of the desired value. Fine tuning of the YIG is accomplished by the output phase lock loop, which supplies a controlled tuning current to the YIG's FM coil. The overall synthesis process can involve up to six phase lock loops, depending on output frequency resolution.

### 3.5.1 Phase Lock Loop

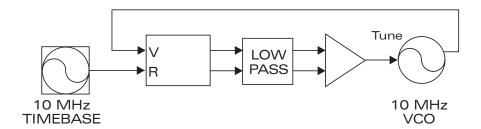

The purpose of a phase lock loop (PLL) is to control a variable frequency oscillator so that its output frequency has the same accuracy and stability as that of a fixed reference oscillator.

The PLL works by comparing two frequency inputs, one fixed and one variable. After comparison, it supplies a correction signal to the variable oscillator achieving and maintaining a constant phase relationship between the two inputs (see Figure 3-4).

Figure 3-4: Elementary Phase Lock Loop

The stability and accuracy of a reference frequency (for example, the signal produced by a 10 MHz crystal oscillator) can be transferred to a voltage controlled oscillator (VCO) by means of a phase lock loop. The 10 MHz signal is applied to the reference input of the PLL, and the VCO output frequency is fed back to the variable input of the PLL. A phase detector in the PLL circuit compares the two inputs and determines whether the variable input is leading, or lagging, the reference. The phase detector has two outputs. Pulses appear at one output, depending on whether the variable input is leading or lagging. (The width of the pulses is proportional to the degree of phase difference.) The width of the pulses are averaged by a low pass filter and DC amplifier; the result is a correction signal causing the VCO frequency to increase, or decrease, in order to reduce the phase difference between the two input frequencies. When the phase error is eliminated: the frequencies are equal, the loop is said to be locked, and the VCO frequency acquires the accuracy and stability of the reference input.

Although the variable input to the phase detector should equal the frequency of the reference input, it need not equal the frequency of the VCO. If a frequency divider is introduced between the VCO and the variable input, the VCO can be run at a frequency that is a multiple of the reference frequency. For example, if the VCO output is divided by ten before being applied to the phase detector input, the VCO can run at 100 MHz and still be phase locked to a 10 MHz reference. A frequency divider intervening between the VCO and the phase detector variable input is called a prescaler. If the prescaler is programmable (i.e., it can be set to a given divisor), a variety of frequencies can be phase locked to a single reference frequency (see Figure 3-5).

Figure 3-5: Phase Lock Loop, with Prescaler

Since the output frequency must be some multiple of the reference frequency input to the phase detector; the reference frequency limits the resolution of the system. For example: using a 10 MHz timebase, frequencies of 70 MHz, or 80 MHz, can be generated. However, frequencies of 73 MHz cannot be generated, because digital frequency dividers can perform integer divisions only (i.e., the prescaler cannot be programmed to divide by 7.3). Nevertheless, if the reference frequency applied to the phase detector is itself programmable, this difficulty can be overcome. The solution is to use a 1 MHz reference frequency and divide the output by 73, or use a 7.3 MHz reference and divide the output by 10.

### 3.5.2 Microwave Frequency Synthesis

Digital synthesis of microwave frequencies is impeded by two inherent difficulties. First, these frequencies are well above the operating range of digital logic circuits. Secondly, the bandwidths required tend to be large (several thousand Megahertz). A requirement for fine frequency resolution over so wide of a range further complicates the synthesis process.

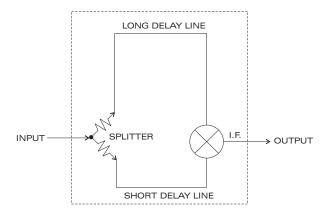

Because the Synthesizer output frequency is too high for digital circuits to work with, the Synthesizer uses RF mixers to downconvert microwave signals to a lower and more workable range. Generally, a mixer provides an intermediate frequency equal to the difference between two high-frequency inputs. For example, a step-recovery diode multiplier and an RF mixer (used in a combination known as a sampling mixer) can derive a low frequency I.F. equal to the difference between the output microwave signal and some harmonic of a stable reference frequency. The various reference signals used to synthesize the output are generated at, or mixed down to, frequencies low enough to drive digital circuits.

The problem of bandwidth, insofar as it limits frequency resolution, is overcome through the use of several compounded PLL circuits, which produce reference frequencies programmable in 1 kHz increments over a wide range.

### 3.5.3 The Synthesis Network

All output frequencies are synthesized by the output PLL, and are ultimately phase locked to the 10 MHz master reference. The Synthesizer can be analyzed as two parallel branches connecting the master reference to the output PLL reference and variable inputs. The variable branch includes feedback from the output YIG oscillator. *Unless otherwise noted all circuits are located in the Synthesizer module*.

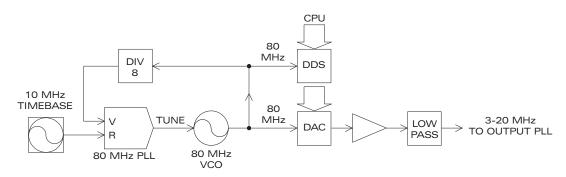

#### 80 MHz PLL (A1)

The 80 MHz PLL is used to generate a fixed 80 MHz output which is phase locked to the timebase. The 80 MHz VCO is tuned by the output of a phase comparator. The VCO output is fed back to the phase comparator's variable input by way of a divide-by-eight circuit (so that the variable input is 10 MHz when the loop is locked). The phase comparator's reference input is the 10 MHz timebase.

The fixed 80 MHz output of the VCO is used as a reference input by the Direct Digital Synthesizer (DDS) chip. The DDS is used in conjunction with a Digital-to-Analog Converter to generate a programmable output frequency in the range of 3 to 20 MHz. The output frequency is programmed digitally by the CPU; the DDS generates a sequence of digital values which is converted into a waveform by the DAC. (The DAC, too, is clocked by the 80 MHz reference input.) The DAC's output is amplified and furnished (through a low-pass filter which removes noise generated by the digital circuits) to the reference input of the Output PLL.

Figure 3-8: 80 MHz PLL and DDS

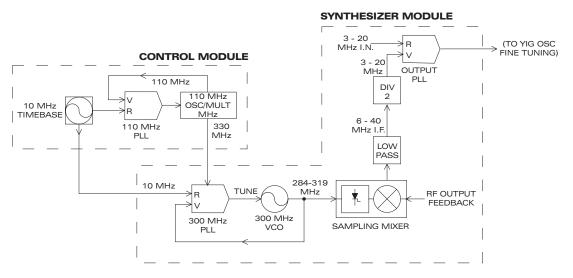

#### 3.5.5 The Variable Branch

This branch consists of circuits in the following sequence:

10 MHz master reference (Control module)

110 MHz PLL (Control module)

110 MHz oscillator/multiplier (Control module)

300 MHz PLL (A2)

300 MHz VCO/driver (A104)

Sampling mixer/IF amplifier (A104)

Divide-by-N (A2)

Output PLL, variable input (A2)

Figure 3-9: The Variable Branch

The 10 MHz master reference and the 110 MHz PLL are the same circuits used in the reference branch.

The 110 MHz oscillator/multiplier supplies a 330 MHz reference input to the 300 MHz PLL.

The 300 MHz PLL and the 300 MHz VCO/driver function together as a programmable source, generating frequencies in 1 MHz steps between 284 and 319 MHz (the 300 MHz PLL/VCO combination is described in more detail on the following page). This 284 to 319 MHz output is amplified and furnished to the multiplier input of the sampling mixer.

The sampling mixer has a step recovery diode multiplier on one of its inputs (the input driven by the 300 MHz VCO): the multiplier produces a series of frequency components that are harmonics of the input. The other input to the mixer is an RF feedback signal, coupled from the output of the YIG oscillator. The mixer combines the YIG frequency with the harmonics of the VCO frequency, yielding a great variety of intermediate frequency (IF) components. The IF output is amplified and filtered in order to pass only IFs within an 80 MHz range. In this way the output is limited to a single IF component

derived from the difference between the YIG frequency and one of the VCO's harmonics. The IF (a signal programmable over a range of 6 to 40 MHz) is applied to the divide-by-2 circuit.

The divide-by-2 circuit produces an output frequency in the range of 3 to 20 MHz. The output is applied to the variable input of the output phase lock loop. The amplified and filtered phase detector output of the PLL is further amplified by the FM driver circuit before being applied to the YIG's FM coil. The YIG is tuned in order to adjust the sampling mixer's IF and thus equalize the reference and variable inputs to the PLL.

The various programmable frequencies are set by the Synthesizer Control module, in accordance with a complex algorithm, to produce the requested output frequency.

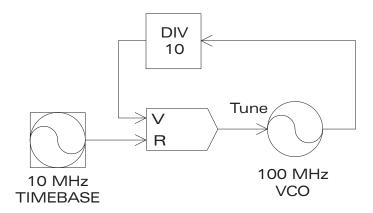

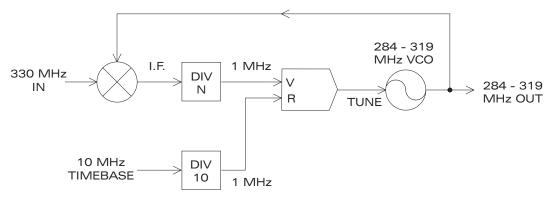

#### 300 MHz PLL/VCO

The 300 MHz PLL/VCO portion of the variable branch consists of an oscillator, a mixer, two dividers, and a phase comparator (see Figure 3-10). The VCO's frequency output is fed back to the mixer, and mixed with the 330 MHz reference input. The resulting IF equals the difference between the VCO's frequency and 330 MHz; since the VCO has a range of 284 to 319 MHz, the IF has a range of 11 to 46 MHz.

The IF is furnished to a programmable divider. The divider is programmed with whatever divisor is needed to reduce the desired IF to 1 MHz (in other words, if the desired IF is 25 MHz, the divisor is set to 25). The 1 MHz output of the divider is applied to the variable input of the phase comparator (of course, the output of the divider will equal 1 MHz only when the loop is locked).

The reference input to the phase comparator is a fixed 1 MHz signal, produced by dividing the 10 MHz timebase signal by ten. The comparator's output drives the VCO in whatever direction will reduce the difference between the fixed 1 MHz input and the output of the divider.

The frequency of the VCO is determined by the setting of the programmable divider. If the divisor is set to 11, the VCO will be driven by the phase comparator to 319 MHz, resulting in an 11 MHz IF and a 1 MHz input to the phase comparator. If the divisor is set to 46, the VCO will be driven to 284 MHz, resulting in a 46 MHz IF and a 1 MHz input to the phase comparator.

Figure 3-10: 300 MHz PLL/VCO

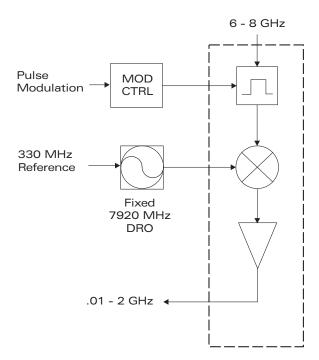

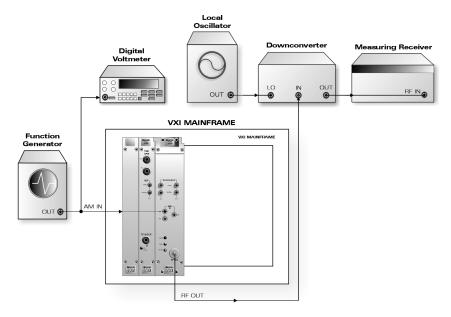

#### 3.5.6 The Downconverter

The downconverter extends the frequency range of the Synthesizer module downwards, to 10 MHz. The downconverter is needed because its .01 to 2 GHz range is too low to be generated by a YIG oscillator (see Figure 3-11). The downconverter circuit mixes the YIG frequency with the fixed output of a local oscillator, yielding an intermediate frequency output in the range of .01 to 2 GHz.

The downconverter circuit is part of the main RF module. During operation below 2 GHz, a coupler in the output path diverts some RF from the module to the downconverter; the low frequency signal synthesized by the downconverter is returned to a switch and furnished to the step attenuator.

During operation in the downconverter range, the YIG oscillator is tuned to a frequency in the approximate range of 5.9 to 7.9 GHz. The downconverter switch furnishes this frequency to the downconverter mixer. The other input to the mixer is a fixed 7.920 GHz input from a Dielectric Resonant Oscillator (DRO). The DRO output is phase-locked to the 330 MHz reference signal applied to it; the 330 MHz reference is in turn phase-locked to the instrument's 10 MHz master reference.

The IF output from the mixer is equal to the difference between the YIG frequency and the 7.920 GHz fixed output of the DRO. For example, the IF is 1.000 GHz when the YIG frequency is 6.920 GHz; the IF is .01 GHz when the YIG frequency is 7.910 GHz). The computer tunes and locks the YIG oscillator to the frequency that will yield the desired IF output from the downconverter mixer. The IF is amplified and returned to the downconverter switch.

Instrument functions, including level control and modulation, operate normally in the downconverter range (the leveling and modulation of the RF input to the downconverter mixer from the RF module is reflected in the mixer's IF output). The frequency synthesis process for the YIG frequency is also normal, except that it yields a frequency equal to 7.920 GHz minus the required output frequency.

Figure 3-11: Downconverter Circuit

### 3.6 Circuit Descriptions (Controller)

### 3.6.1 VXI/Interface Control (A1)

This PC assembly is the only assembly in the Series 50000B that actually talks on the VXI bus. The A1 board holds the DT9150 Interface Technology daughter card, which handles all VXI Bus interface and communication. L1 thru L4 and associated capacitors provide filtering of the +5V supply to this assembly.

In addition to providing VXI bus interface functions, the microprocessor on this board runs the software contained in the U6 and U7 PROMS to control the 50000B modules. This software uses the U13 Peripheral Interface Timer IC 68230 to send and receive data over the VXI Local bus (via U11) to the various 50000B modules in the system. U13 also provides the control signals such as address data strobes and Direction strobe to control the Data bus. U9 supplies address decoding for U13. U10 provides the DTACK signal for the operation of U13.

### 3.6.2 110 MHz Assembly (A101A1)

#### 110 MHz Phase Lock Loop

The function of this circuit is to phase lock the 110 MHz VCO on the oscillator/multiplier board to the 10 MHz master reference. In addition, this circuit performs important functions related to the master reference itself.

The output frequency of the 110 MHz VCO is received at J8 and U2 divides the input by 11. When the loop is locked, the input is exactly 110 MHz, and the divider output is exactly 10 MHz. One output from U2 is applied to the variable input of the phase comparator at U5-9. The other is buffered by U1C and serves as the 10 MHz reference signal out of the 52000B front panel. The reference input to the phase comparator comes from the 10 MHz input/output circuit.

The reference input to the phase comparator U5-6 comes from a switching circuit, which selects either an internal or external 10 MHz reference. When no external reference is present at J12, the internal 10 MHz reference at J10, buffered by U1B, propagates through U4C and the phase comparator (U5-6). When an external 10 MHz signal is present at J12, it is buffered by U1A and propagates through U4A to the phase comparator. The presence of an external 10 MHz reference is detected when a charge is built up on C24 and the switching circuit (comparator U8) switches to a high state. This causes U6 output to go high and turn off the supply to the internal 10 MHz reference. The switching circuit enables the external reference path at U4A and disables the internal reference at U4C. The selected reference is then available through Q3 and Q4 as the 10 MHz (Timebase) reference output on the 52000B front panel.

When its reference and variable inputs are not in phase, U5 produces wide pulses at one of its outputs, depending on whether the variable input is leading or lagging the reference. The pulsed outputs are filtered and amplified by U3-7 to produce a voltage output (J11) which tunes the 110 MHz VCO.